Note: All project files are available on GitHub: Hardware Design and FPGA HDL Sources.

Cologne Chip is a refreshing newcomer to the FPGA market. Their first FPGA device, the GateMate, offers a compelling middle ground for developers: it provides a respectable amount of logic resources at a highly competitive price point (approximately 15 EUR in volume). Furthermore, as it is manufactured in Germany, it presents an interesting alternative for those navigating global supply chain complexities.

What sets the GateMate apart from established competitors is its toolchain strategy. Rather than forcing developers into a proprietary environment, Cologne Chip has fully embraced the open-source Yosys/nextpnr ecosystem. This accessibility makes it an attractive platform for rapid prototyping and open-source hardware development.

HDMI Electronics

My initial goal was to implement HDMI / DVI output. These standards rely on Transition-Minimized Differential Signaling (TMDS), a physical layer standard that the GateMate’s I/O pins do not natively support.

While previous community projects have demonstrated that lower resolutions (like 640×480) can be achieved by driving the TMDS lanes through a resistor from the FPGA I/Os, this “hack” lacks the signal integrity required for higher bandwidths. To achieve stable Full-HD (1080p) output, a more robust hardware solution was necessary.

I opted for a dedicated Parallel RGB to TMDS converter, specifically the TFP410 from Texas Instruments. This IC handles the high-speed differential signaling, allowing the FPGA to interface via a standard parallel bus.

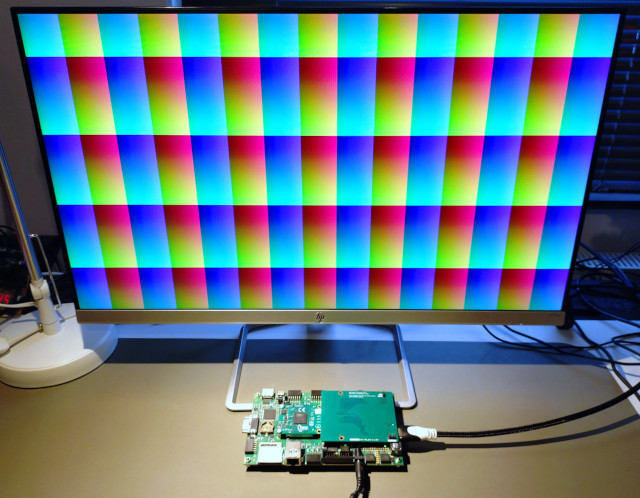

For the controller, I used the Trenz Electronic TEG2000 SOM, which features the GateMate A1 FPGA. I paired this with a TE0701 carrier board that I already had laying around. The carrier offers a 320-pin FMC connector that can be used to connect custom high-speed electronics. Hence, I designed a custom 4-layer (for signal integrity) PCB that hosts the TFP410 and plugs into the FMC port. This board also features a MIPI input and HyperRAM, which I plan to use for future video processing tasks. All hardware design files are available in the GitHub repository linked above.

FPGA Implementation

Implementing 1080p at 60 Hz requires a pixel clock of 148.5 MHz (per CEA-861 standards). During development, it became clear that the GateMate logic fabric – particularly in the “Economy” power mode used on the Trenz SOM – struggles to meet timing at these frequencies.

To circumvent this performance ceiling, I implemented a dual-pixel parallel architecture:

Parallel Processing: The internal logic processes two pixels per clock cycle, effectively cutting the required operating frequency in half to 74.25 MHz.

DDR Output: The data is serialized at the output pins using Double Data Rate (DDR) buffers to maintain the required throughput.

Clock Management: I utilized the GateMate’s integrated PLL to generate two phase-aligned clocks simultaneously: one at 74.25 MHz for the internal logic and one at 148.5 MHz for the video output synchronization.

Resource Usage

The resource footprint for this Full-HD design – which includes the dual-pixel logic, timing controllers, and a synthetic test pattern generator – is remarkably small. Even when driving a 1080p signal, the design occupies only a fraction of the available logic on the CCGM1A1, leaving ample room for complex video processing or soft-cores.

| Resource | Usage | Available | Percentage |

|---|---|---|---|

| PLL: | 1 | 4 | 25% |

| CPE_LT: | 370 | 40960 | <1% |

| CPE_FF: | 168 | 40960 | <1% |

| CPE_RAMIO: | 63 | 40960 | <1% |

Conclusion

By utilizing a dual-pixel path and an external transmitter, I successfully generated a stable 1080p @ 60 Hz signal. While the GateMate may not match the raw performance of high-end (and significantly more expensive) FPGAs, its affordability and open-source compatibility make it a strong candidate for cost-sensitive applications.

The VHDL source code is available on GitHub (see above) and can be easily adapted for other video-centric GateMate projects.